4.2.6. Звуковой процессор

Звуковой процессор приставки SONY PLAYSTATION служит для формирования звукового сопровождения, освобождая тем самым ресурсы центрального процессора для других целей. Отличие данного модуля от рассмотренных выше заключается в том, что, помимо обычной программной генерации различных звуков, игровая приставка SONY PLAYSTATION позволяет воспроизводить аудиофайлы с компакт-дисков в формате Audio CD. В этом разделе приводится краткое описание архитектуры звукового процессора и его регистров.

Микросхема звукового процессора игровой приставки SONY PLAYSTATION поддерживает работу 24 независимых аудиоканалов, дает возможность генерировать стереофоническое звучание и микшировать его с аудиосигналом, получаемым с CD-ROM. Привод CD-ROM управляется через операционную систему приставки (данная тема в настоящей книге не рассматривается из-за большого объема материала). Чтобы ускорить работу звукового процессора, применяется ОЗУ объемом 512 Кб, предназначенное для хранения звуковых данных. ОЗУ звукового процессора

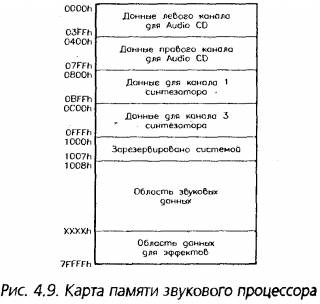

В документации ОЗУ звукового процессора называется звуковым буфером (Sound Buffer), мы в дальнейшем также будем использовать этот термин.

Данные в ОЗУ хранятся в виде компрессированных блоков, за каждым из которых закреплено 16 байт. Два байта здесь занимает заголовок, содержащий служебную информацию, а остальные 14 байт отводятся под сведения о формируемом аудиосигнале. При декомпрессии блока эти 14 байт преобразуются в 28 байт, передаваемых звуковому процессору.

Первые 4 Кб памяти играют роль буфера для хранения декодированных звуковых данных, поступающих от CD-ROM, а также данных каналов 1 и 3, воспроизводимых звуковым процессором. Информация в этих областях хранится в виде 16-разрядных чисел, по одному числу на такт воспроизведения. Тактовая частота формирования звукового сигнала в игровой приставке составляет 44,1 кГц.

Следующие 4104 байт зарезервированы системой и используются звуковым процессором в собственных целях.

С адреса 1008h начинается область аудиоданных, а за ней находится область обработки спецэффектов. Размеры этих областей меняются в зависимости от того, задействован ли блок спецэффектов и какие именно спецэффекты применяются.

Распределение адресного пространства звукового процессора игровой приставки SONY PLAYSTATION показано на рис. 4.9.

Рис. 4.9. Карта памяти звукового процессора Формирование звукового сигнала

Как уже упоминалось, звуковой процессор игровой приставки имеет 24 независимых канала любой из них может создавать звуковой сигнал, генерировать шум или частоту модуляции для другого канала. Кроме того, каждый канал включает программируемый ADSR-фильтр огибающей. Работа ADSR-ФИЛЬтра поясняется на рис. 4.10.

Процесс формирования звукового сигнала делится на несколько фаз:

1. НАРАСТАНИЕ СИГНАЛА (А). СИГНАЛ НАРАСТАЕТ ОТ НУЛЕВОГО ЗНАЧЕНИЯ ДО МАКСИМУМА.

2. ПОНИЖЕНИЕ УРОВНЯ (D). УРОВЕНЬ ЗВУКОВОГО СИГНАЛА ПОНИЖАЕТСЯ ДО ОСНОВНОГО УРОВНЯ.

Рис. 4. 10. ADSR-фильтр огибающей звукового сигнала 3. Основное звучание (S). В течение заданного времени генерируется сигнал, уровень которого может понижаться или повышаться.

4.3атухание (R). Уровень сигнала снижается до нуля. Регистры звукового процессор

С точки зрения программирования звуковой процессор игровой приставки SONY PLAYSTATION представляет собой набор регистров, занимающих в адресном пространстве приставки диапазон 1F801C00h - 1F801DFFh. Все регистры звукового процессора являются 16-разрядными.

Сначала идут 24 группы по восемь 16-разрядных регистров, каждая из таких групп предназначена для управления одним каналом. Поскольку все группы аналогичны, мы рассмотрим только одну из них. Регистр громкости левого канала

Адрес: 1F801xx0h.

Назначение разрядов.

Регистр используется для установки громкости и настройки генератора Назначение разрядов в этих режимах различно и описывается ниже.

В РЕЖИМЕ НАСТРОЙКИ ГРОМКОСТИ:

D15 - выбор режима, должен быть равен 0.

D14 - фаза сигнала

0 - нормальная;

1 - инверсная.

D13 - D0 - громкость сигнала.

В РЕЖИМЕ НАСТРОЙКИ ГЕНЕРАТОРА:

D15 - выбор режима должен быть равен 1.

D14 - режим изменения сигнала:

0 - линейное изменение;

1 - экспоненциальное изменение.

D13 - направление изменения уровня сигнала

0 - увеличение;

1 - уменьшение.

D12 - фаза сигнала

0 - нормальная;

1 - инверсная.

Указанная здесь фаза должна совпадать с фазой, заданной при настройке громкости.

D11 - D7 - не используются.

D6 - D0 - приращение уровня сигнала. Регистр громкости правого канала

Адрес: 1F801xx2h.

Назначение разрядов.

Регистр аналогичен регистру громкости левого канала. Регистр высоты звука

Адрес: 1F801xx4h.

Назначение разрядов.

В разряды D13 — D0 регистра записывается значение, определяющее высоту генерируемого звука. Разряды D15 и D14 не используются. Регистр адреса звуковых данных

Адрес: 1F801xx6h.

Назначение разрядов.

В регистр записывается адрес начала воспроизводимых данных в ОЗУ звукового процессора, деленный на 8. Регистр 1 настройки огибающей

Адрес: 1F801xx8h. Назначение разрядов.

Регистр используется для настройки огибающей формируемого аудиосигнала, изображенной на рис. 4.22.

D15 - режим нарастания:

0 - линейный;

1 - экспоненциальный.

D14 - D8 - код, задающий время нарастания сигнала (Ar на рис. 4.22).

D7 - D4 - код, определяющий время понижения уровня (Dr на рис. 4.22). Понижение уровня всегда происходит в экспоненциальном режиме.

D3 - D0 - код уровня сигнала основного звучания (S1 на рис. 4.22). Регистр 2 настройки огибающей

Адрес: 1F801xxAh.

Назначение разрядов.

Регистр применяется для настройки огибающей формируемого аудиосигнала, изображенной на рис. 4.22.

D15 - режим изменения основного звучания:

0 - линейный;

1 - экспоненциальный.

D13 - направление изменения сигнала основного звучания:

0 - нарастание;

1 - затухание.

D12 - не используется.

D11 - D6 — код, задающий время основного звучания (Sr на рис. 4.22). D5 - режим затухания:

0 - линейное;

1 - экспоненциальное.

D4 - D0 - код, указывающий время затухания сигнала (Rr на рис. 4.22). Регистр текущего уровня огибающей

Адрес: 1F801xxCh.

Назначение разрядов.

При чтении из регистра программа получает информацию о текущем уровне огибающей сигнала данного канала. Регистр адреса повтора

Адрес: 1F801xxEh.

Назначение разрядов.

В регистр помещается деленный на 8 адрес, с которого следует начать повторное воспроизведение звуковых данных. Адрес нужно записывать во время проигрывания звука, поскольку при запуске генератора в регистре будет 0.

Далее идет группа регистров, предназначенная для управления звуковым процессором игровой приставки в целом. Регистр уровня сигнала левого канала

Адрес: 1F801D80h.

Назначение разрядов.

Код, записываемый в регистр, определяет уровень выходного сигнала для левого канала. Выходной сигнал получается после микширования сигналов всех левых каналов звукового процессора. Регистр уровня сигнала правого канала

Адрес: 1F801D82h.

Назначение разрядов.

Код, записываемый в регистр, определяет уровень выходного сигнала для правого канала. Выходной сигнал получается после микширования сигналов всех правых каналов звукового процессора. Регистр глубины реверберации левого канала

Адрес: 1F801D84h.

Назначение разрядов.

Код, записываемый в регистр, определяет параметры реверберации сигнала для левого канала. D15 - фаза сигнала:

0 - нормальная;

1 - инверсная.

D14 - D0 - громкость эффекта. Регистр глубины реверберации правого канала

Адрес: 1F801D86h.

Назначение разрядов.

Код, записываемый в регистр, определяет параметры реверберации сигнала для правого канал D15 - фаза сигнала:

0 - нормальная;

1 — инверсная. D14 - D0 - громкость эффекта. Далее следуют группы по два 16-разрядных peгистра, которые предназначены для управления отдельными каналами звукового процессора Каждый разряд записываемого сюда значения управляет отдельным стереофоническим каналом. Так, например, для контроля канала 0 используется разряд DO первого регистра в паре, каналом 1 управляет разряд D1, каналом 2 - разряд D2 и так далее до канала 15, которому соответствует разряд D15. Каналами 16-23 управляют, устанавливая или сбрасывая разряды второго регистра в паре. При этом для канала 16 применяется разряд D0, для канала 17 - разряд D1 и т.д. Старшие восемь разрядов второго регистра не используются и должны быть равны 0. Регистры включения каналов звукового процессора

Адрес: 1F801D88h, 1F801D8Ah.

Назначение разрядов.

Установка в 1 какого-либо разряда в этих регистрах приведет к включению соответствующего аудиоканала. Регистры выключения каналов звукового процессора

Адрес: 1F801D8Ch, 1F801D8Eh.

Назначение разрядов.

Установка в 1 какого-либо разряда в этих регистрах приведет к выключению соответствующего аудиоканала. Регистры включения режима частотной модуляции

Адрес: 1F801D90h, 1F801D92h.

Назначение разрядов.

Чтобы канал звукового сопровождения работал в режиме частотной модуляции, необходимо установить в 1 соответствующий разряд. В качестве частоты модуляции используется выходной сигнал предыдущего канала. Регистры включения генератора шума

Адрес: 1F801D94h, 1F801D96h.

Назначение разрядов.

Установкой 1 в соответствующем разряде этим регистров канал звукового сопровождения можно перевести в режим генератора шума. Регистры включения режима реверберации

Адрес: 1F801D98h, 1F801D9Ah.

Назначение разрядов.

Установкой 1 в соответствующем разряде канал звукового сопровождения можно перевести в режим реверберации. Регистры контроля работы каналов

Адрес: 1F801D9Ch, 1F801D9Eh.

Назначение разрядов.

Регистры доступны для чтения и используются для контроля работы каналов звукового процессора. Когда канал занят формированием аудиосигнала, соответствующий ему разряд установлен в 1. Если же канал находится в режиме ожидания, разряд равен 0. 4.3. Принципиальная схема

Итак, мы познакомились с программной архитектурой игровой приставки SONY PLAYSTATION, которая, как и ожидалось, гораздо сложнее, чем у остальных описанных в книге устройств. Данный раздел посвящен описанию аппаратной части и принципов работы SONY PLAYSTATION.

Конструктивно приставка SONY PLAYSTATION выполнена на трех платах. На первой плате расположена собственно игровая приставка, схема которой разделена на следующие функционально законченные блоки: модуль центрального процессора, модуль графического процессора, модуль звукового процессора и модуль контроллера привода CD-ROM. К плате центрального процессора подключается вторая плата - модуль адаптации, предназначенный для работы с компакт-дисками различных производителей. На третьей плате выполнен импульсный блок питания. 4.3.1. Модуль центрального процессора

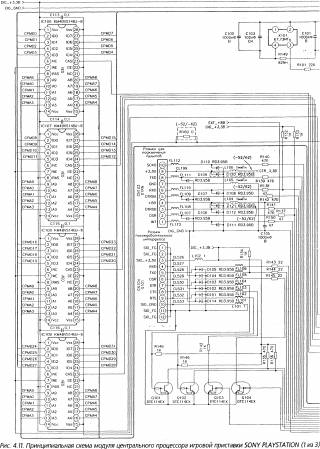

Рассмотрение схемы игровой приставки мы начнем с модуля центрального процессора. Его принципиальная схема изображена на рис. 4.11.

Основой процессорного модуля SONY PLAYSTATION является микросхема IС103 (CXD8606AQ), объединяющая RISC-ядро центрального процессора и контроллер ввода/вывода. Микросхема выполнена в корпусе для поверхностного монтажа с 208-выводами.

Работа центрального процессора синхронизируется внутренним тактовым генератором, частота которого стабилизирована кварцевым резонатором Х101

(67,73 МГц), подключенным к входу CRYSTALP (вывод IC103/4). Тактовая частота около 33,9 МГц для работы RISC-ядра процессора формируется Внутренним делителем.

Посредством шины данных DD0 - DD31 (выводы IС103/42-40,37-28,25-16,23-31), шины адреса DA0 - DA11 (выводы 1С103/68,67,64-55) и шины управления, образованной цепями передачи сигналов DWE (вывод IC103/43), DRAS0 (вывод IС103/ 45) и DCAS0- DCAS3 (выводы IC103/49-46), к центральному процессору подключено динамическое ОЗУ приставки объемом 2 Мб. ОЗУ выполнено на четырех микросхемах динамической памяти IC106- IC109 (KM4BVC14BJ-6) объемом 512 Кб каждая. В некоторых моделях используется одна микросхема динамического ОЗУ IC106 типа А65844 или А67871, выполненная в 70-выводном корпусе. Для подсоединения этой микросхемы используются те же выводы центрального процессора. Обратите внимание: на шине адреса динамического ОЗУ центрального процессора разряды DA8 (вывод IC103/58) и DA10 (вывод IC103/56) не применяются, а разряды адреса DA9 (вывод IС103/ 57) и DAH (ВЫВОД IC103/55) подключены нестандартным способом. На выходе DA11 формируется разряд адреса СРМА8, а на линии DA9 -разряд СРМА9. Это обусловлено внутренней структурой процессора и картой распределения адресного пространства, выбранной фирмой-производителем.

Работа центрального процессора с динамическим ОЗУ происходит обычным образом. Сначала на шину адреса подаются девять младших разрядов адреса, сопровождаемые сигналом низкого уровня на выходе DRAS0, а затем девять старших разрядов адреса ячейки памяти, и на выходах DCAS0 - DCAS3 формируется сигнал низкого уровня. Одновременно происходит запись или считывание информации из динамического ОЗУ. Выполняемое действие (запись или чтение) определяется уровнем сигнала на выходе DWE центрального процессора. Низкий логический уровень соответствует записи, высокий - чтению данных.

Как в любом динамическом ОЗУ, микросхемы, используемые в игровой приставке, требуют постоянной регенерации хранящейся в них информации. Во время регенерации центральный процессор устанавливает на шине адреса динамического ОЗУ адрес регенерации и генерирует на выходе DRAS0 сигнал низкого логического уровня. Поскольку в течение этого сигнала на все выходы CAS микросхем динамического ОЗУ поступает напряжение высокого логического уровня, происходит регенерация ОЗУ, а не чтение или запись.    Рассмотренные выше шины адреса, данных и управления предназначены только для подключения к центральному процессору динамического ОЗУ.

Для подсоединения внешних устройств и обмена информацией с другими блоками игровой приставки используются 16-разрядная системная шина данных SD0 - SD15 (выводы 10103/107-116,119-124) и 23-разрядная системная шина адреса SA0 - SA23 (выводы 10103/125-129,132-142,145-152).

Поскольку графическая система игровой приставки особенно требовательна к скорости передачи данных, обмен информацией между центральным и графическим процессорами в SONY PLAYSTATION осуществляется по отдельной 32-разрядной шине VD0 - VD31 (выводы IС103/161-169Д72-181,184-194,197,198).

Внутреннее ПЗУ приставки IC102 (MSM334031C) объемом 512 Кб, в котором записана операционная система, необходимая для работы системы, подключено к системной шине адреса и восьми младшим разрядам системной шины данных. При обращении к ПЗУ центральный процессор формирует сигнал низкого логического уровня на выходе SRD (вывод IC103/101) и на линии выборки ПЗУ CS2 (вывод IC103/97). Сигнал CS2 подается на вход выбора кристалла микросхемы ПЗУ (вывод IС102/ 22). Сигнал чтения поступает на вход разрешения чтения ОЕ (вывод IС 102/24).

Микросхема центрального процессора IС103 дополнительно генерирует управляющие сигналы, контролирующие обмен информацией с другими модулями игровой приставки.

В модуль графического процессора передаются тактовые сигналы DBLCLK (вывод IC103/206) и SYSCLK0 (вывод IС103/154), предназначенные для синхронизации работы двух процессоров. Посредством сигнала разрешения передачи информации GPUCS (вывод IC103/205), сигнала разрешения записи данных в графический процессор GPUWR (вывод IC103/203) и сигнала разрешения чтения данных из регистров графического процессора GPURD (вывод IC103/204) центральный процессор приставки управляет обменом информацией с графическим процессором. Для этого в зависимости от выполняемой операции (запись или чтение) должен быть установлен низкий логический уровень на выходе GPUCS и на одном из выходов GPURD или GPUWR. Регистр графического процессора, с которым производится обмен, определяется уровнем сигнала на выходе GPUA2 центрального процессора (вывод IС 103/153). Низкий логический уровень соответствует регистру данных, высокий - регистру управления.

Когда для передачи данных используется контроллер прямого доступа к памяти, графический

процессор посылает сигнал запроса на захват шины, устанавливая низкий логический уровень на шине GPUDREQ, подключенной к выводу 200 центрального процессора IC103. Получив такой запрос, процессор освобождает шины, извещая об этом установкой низкого логического уровня на выходе GPUDACK (вывод IC103/202).

От графического процессора на входы центрального поступают тактовый сигнал РСК (вывод IС103/ 160) частотой 13,3 МГц (опорная частота формирования изображения, деленная на 4), сигнал строчной синхронизации HBLANK (вывод IC103/159) и сигнал кадровой синхронизации VBLANK (вывод IC103/199). На вход INTIN1 (вывод IC103/102) подается сигнал GPUINT, низкий уровень которого свидетельствует о том, что графический процессор запрашивает обработку прерывания.

Сигнал начальной установки поступает на вход EXT RESET (вывод IC103/76). Он формируется в блоке питания при включении или при нажатии кнопки RESET. Кратковременный импульс низкого логического уровня приводит к сбросу микропроцессора и остальных контроллеров игровой приставки.

Для управления звуковым процессором центральный процессор вырабатывает четыре сигнала. Звуковой процессор обменивается данными с центральным по сигналу разрешения низкого уровня на выходе SPUCS (вывод IC103/96). Информация при этом передается по системной шине данных, а адрес регистра звукового процессора - по системной шине адреса. Тип операции (запись или чтение) определяется сигналами на выходах SRD (вывод IC103/101) и SWR0 (вывод IC103/100). Сформированный звуковым процессором сигнал запроса на прерывание SPUINT поступает на вход INTIN9 (вывод IС103/90). Сигналы SPUDREQ (вывод IC103/88) и SPUDACK (вывод IС103/87) предназначены для запроса прямого доступа к памяти: звуковой процессор запрашивает прямой доступ путем установки на выходе SPUDREQ сигнала низкого уровня, после чего центральный процессор освобождает шины и сигнализирует об этом низким уровнем на выходе SPUDACK.

Сигналы CDRDCS и CDRDINT управляют декодером информации, поступающей от CD-ROM. Когда центральный процессор обращается к регистрам декодера для чтения или записи данных, он устанавливает низкий логический уровень на шине CDRDCS (вывод IC103/95). По шине CSRDINT запрос на прерывание передается от декодера на вход INTIN2 центрального процессора (вывод IС103/94).

Отдельной задачей микросхемы центрального процессора является координация взаимодействия процессорного модуля с различными устройствами, подключаемыми к разъему параллельного

интерфейса CN103, разъему последовательного интерфейса CN104 и разъему игрового пульта CN102.

На разъем параллельного интерфейса выведены сигналы системной шины данных (контакты CN103/6-13,40-47) и системной шины адреса (контакты CN103/14,15,20-29,48,49,54-63). На контакт 2 этого разъема подается сигнал сброса, служащий для начальной инициализации подсоединенного устройства. Также в распоряжение внешнего устройства, подключаемого к разъему параллельного интерфейса, предоставляется один канал прямого доступа к памяти и один запрос на прерывание. Воспользоваться прямым доступом к памяти можно, подав сигнал низкого уровня на контакт 3 разъема. Когда центральный процессор освобождает шины, он сигнализирует об этом установкой низкого уровня на выходе DACK (контакт CN103/36). Чтобы отправить центральному процессору запрос на прерывание, внешнее устройство должно установить низкий уровень на линии IRQ (контакт CN103/37).

Регистры внешнего устройства отображаются на память центрального процессора, то есть для работы с ними применяются те же команды процессора, что и для ячеек памяти. При обращении к выделенной для этих целей области памяти процессор формирует сигнал низкого уровня на выходе CS0 (вывод IC103/98), подключенном к контакту CN103/4. Дополнительную информацию о выбранном регистре (если их несколько) получают, дешифруя данные на шине адреса. Если процессор осуществляет чтение из регистра внешнего устройства, на линии SRD (контакт CN103/30) вырабатывается сигнал низкого логического уровня. В случае записи в регистры на SWR0 (контакт CN103/64) и SWR1 (контакт CN103/38) формируется сигнал низкого уровня.

Для синхронизации допускается использовать тактовый сигнал SYSCLK1, с вывода IC103/154 поступающий на контакт CN103/32.

Кроме того, на разъем параллельного интерфейса выведены напряжения питания +3,3 В (контакты CN103/17.51) и +8 В (контакты CN103/18,52).

Для соединения двух игровых приставок в режиме сетевой игры чаще всего применяется разъем последовательного интерфейса CN104 На его контакты поступает напряжение +3,3 В (контакт CN104/3) и пары сигналов RXD-TXD, DSR-DTR и CTSRTS, стандартные для последовательных интерфейсов. При связи двух приставок необходимо на вход TXD одной из них подать сигнал с выхода RXD другой и наоборот (на вход TXD - с выхода RXD) и сделать такие же совмещения для оставшихся двух пар (DSR-DTR и CTS-RTS). Иные контакты разъемов соединяются в соответствии со своими номерами (1 к 1, 10 к 10 и т.д.). Данные передаются по цепи TXD (контакт CN103/5), а принимаются по цепи RXD (контакт CN103/4). Эти сигналы

поступают непосредственно с выводов процессора IC103/74 и IC103/75. Управляющие сигналы, пересылаемые по цепям DSR (контакт CN104/6), DTR (контакт CN104/7), CTS (контакт CN104/8) и RTS (контакт CN104/9) проходят через буферные усилители на транзисторах Q101 - Q104. Диоды D101 - D105, D114 и ВЧ дроссели FL101 - FL106 используются для защиты от бросков напряжения и сглаживания возникающих помех в последовательном интерфейсе. Дроссели L101 и L102 установлены на шинах питания.

Пульты игровой приставки подключаются к разъемам коммутационной платы, которая в свою очередь соединена с разъемом CN102 процессорного модуля.

От центрального процессора на разъемы для подключения пультов поступают сигналы выбора пульта DTR0A (контакт CN102/5) и DTR0B (контакт CN102/3), сигнал тактовой частоты SCK0 (контакт CN102/10) и данные, передаваемые на пульт (контакт CN102/8). Центральный процессор получает от пульта запросы на прерывание INT (контакт CN102/ 1), DSR (контакт CN102/2) и пакет с информацией

о нажатых на пульте кнопках по цепи RXD (контакт CN102/6). Кроме того, на разъем выведены напряжения питания +8 В (контакт CN102/4) и +3,3 В (контакт CN102/9). Для защиты от перегрузок и помех, как и в последовательном интерфейсе, используются диоды и ВЧ дроссели в цепях питания. 4.3.2. Модуль графического процессора

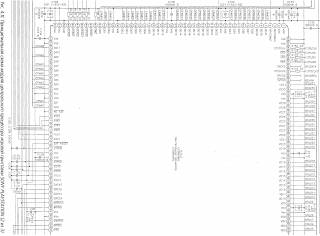

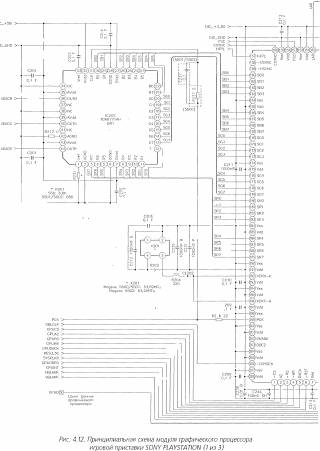

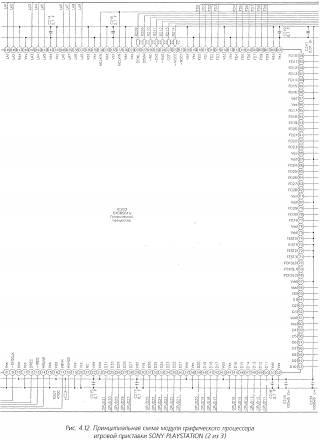

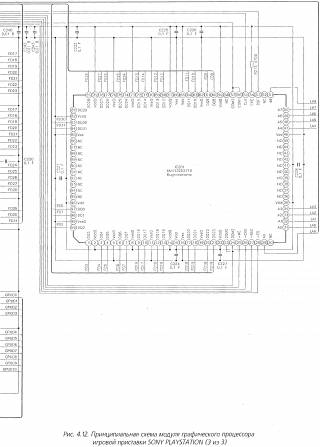

Рассмотрим модуль графического процессора игровой приставки SONY PLAYSTATION, формирующий видеосигнал. Его принципиальная схема приведена на рис. 4.12.

Обработкой графической информации в приставке SONY PLAYSTATION занимается микросхема графического процессора IC203 (CXD8561Q). Как и в большинстве игровых приставок, видеопроцессор является заказной микросхемой и не имеет аналогов. Данные, необходимые при формировании изображения, хранятся в видеопамяти, в качестве которой применяется микросхема 32-разрядного динамического ОЗУ типа SGRAM IC201 (KM4132G2710) объемом

1 Мб. Вместо указанной могут использоваться микросхемы (Мю) μPD481850GF-A12 или μPD481850-A10. Микросхема IC202 (TDA8771AH) представляет собой трехканальный ЦАП, преобразующий 24-разрядный цифровой код от графического процессора в три аналоговых сигнала основных цветов.

Обмен данными между графическим и центральным процессорами приставки происходит по 32-разрядной шине данных GPUD, подключенной к выводам IC203/24-28.31-36,39-42,45-50,53-59,62-65.     Регистр графического процессора, с которым производится обмен, выбирается в зависимости от уровня сигнала на шине адреса GPUA2 (вывод IC203/2). Также от центрального процессора поступают тактовые сигналы DBLCLK (вывод IC203/206), SYSCLK0 (вывод IC203/9) и управляющие сигналы GPUCS (вывод IC203/1), GPURD (вывод IC203/3), GPUWR (вывод IC203/4), RES (вывод IC203/6) и GPUDACK (вывод IC201/5). Назначение этих сигналов было описано в предыдущем разделе.

От графического процессора к центральному передаются сигнал тактовой частоты 13,3 МГц РСК (вывод IC203/199), сигналы кадровой VBLANK (вывод IC203/17) и строчной HBLANK (вывод IC203/14) разверток, сигнал запроса на прерывание GPUINT (вывод IC203/13) и сигнал запроса на захват шин GPUDREQ (вывод IC203/12).

Работа внутренних схем графического процессора, отвечающих за формирование выходных сигналов развертки, тактируется внутренним генератором, частота которого стабилизирована кварцевым резонатором Х201 (53,69 МГц).

Видеопамять обменивается информацией с графическим процессором игровой приставки посредством 32-разрядной шины данных FD0 - FD31,9-разрядной шипы данных LAO - LA9 и сигналов управления RAS (вывод IC201/27), CAS (вывод IC201/26), WE (вывод IC201/25) и CS (вывод IC201/28). Сигнал низкого уровня па входе CS разрешает обмен данными с видеопамятью. При этом производимая операция определяется уровнем сигнала на входе WE (низкий логический уровень соответствует записи). Адрес передается от графического процессора к видеопамяти в мультиплексном режиме, обычном для динамических ОЗУ. Сначала по шине адреса пересылаются младшие девять разрядов адреса, сопровождаемые сигналом RAS низкого логического уровня, затем старшие девять разрядов, которые запоминаются по спаду сигнала CAS. Регенерация памяти происходит автоматически и занимает 1024 цикла (16 мс).

Микросхема видеопамяти позволяет максимально быстро изменять сохраненные данные. Для этого в пей предусмотрены регистры цвета, маски и управления. Помещая определенные команды в регистр управления, можно постранично записывать и считывать данные, производить ускоренную очистку памяти и другие действия над содержимым видеопамяти.

Микросхема IC202 представляет собой трехканальный ЦАП, задачей которого является преобразование получаемых от графического процессора 8-разрядных кодов в аналоговые значения трех основных цветовых составляющих. Данные от графического процессора передаются по трем 8-разрядным шипам: SB0 - SB7 (для кода синего цвета), SG0 - SG7 (для кода зеленого цвета) и SR0 - SR7 (для кода красного цвета). Микросхема трансформирует полученные коды в аналоговые значения напряжения на выходах OUTB (вывод IC202/36), OUTG (вывод IC202/40) и OUTR (вывод IС202/ 44). Напряжения здесь изменяются от 0,2 В (когда на все входы соответствующего капала ЦАП поступают сигналы низкого логического уровня) до 3,2 В (когда на все входы капала подается сигнал высокого логического уровня). Работа цифро-аналогового преобразователя тактируется сигналом РСК, снимаемым с выхода IC203/199 графического процессора.

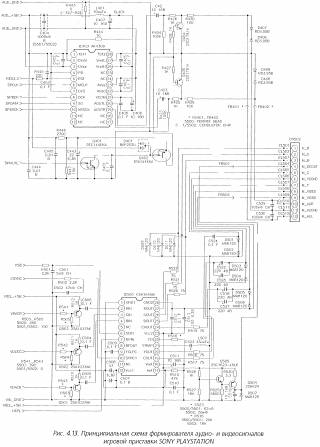

На рис. 4.13 приведена принципиальная схема формирователя аудио и видеосигналов, преобразующего получаемые данные в сигналы на выходном разъеме приставки. Формирователь звуковых сигналов описывается в следующем разделе, а сейчас мы рассмотрим только ту часть схемы, которая генерирует полный видеосигнал.

Формирование низкочастотного телевизионного сигнала игровой приставки SONY PLAYSTATION происходит в микросхеме IC501 (СХА1645М). Сигналы с выходов ЦАП IC202 поступают па входы формирователя IC501 (выводы IC501/2-4) через эмиттерные повторители на транзисторах Q501 -Q503. Они предназначены для согласования уровня выходных сигналов ЦАП (находящихся в пределах 0,2-3,2 В) с входными уровнями микросхемы 1С501 (0-1 В). Кроме того, от графического процессора приходят сигналы тактовой частоты 4,443 МГц (вывод IC501/6), смесь кадровых и строчных синхроимпульсов CSYNC (вывод IC501/10) и логический сигнал NTPL (вывод IC501/7), определяющий кодировку формируемого видеосигнала (NTSC или PAL). В некоторых моделях сигнал NTPL не используется и вывод IC501/7 соединен через конденсатор с общим проводом.

С выходов формирователя IC501 снимается шесть сигналов, подающихся на выходной разъем CN502 видеоприставки. Сигнал M_VIDEO (вывод IС501/ 24) - это низкочастотный полный телевизионный сигнал стандарта PAL пли NTSC амплитудой около 1,5 В. С выходов COUT (вывод IC501/19) и YOUT (вывод IC501/20) снимаются раздельные цветовая и яркостная составляющие видеосигнала. Также микросхема генерирует выходные сигналы трех цветовых составляющих ROUT (вывод IC501/27), GOUT (вывод IC501/26) и BOUT (вывод IC501/25). Сигналы поступают на контакты выходного разъема CN501 через согласующие резисторы R517 - R521 (75 Ом). Видеосигнал проходит через разделительные конденсаторы С518, С527, яркостная составляющая - через конденсаторы С522, С528, а цветовая составляющая — через конденсатор С524. Стабилитроны D501 - D511 (МА8120) установлены для защиты выходных цепей приставки от скачков

напряжения и статического электричества. Вместо них можно использовать любые стабилитроны на напряжение 4,7 В. 4.3.3. Модуль декодера и звукового процессора

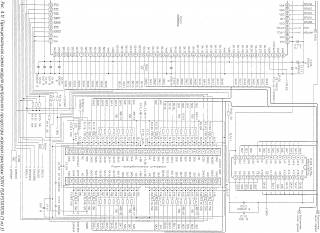

Модуль декодера осуществляет преобразование информации, полученной от контроллера CD-ROM, в цифровые данные, передаваемые затем центральному процессору. Звуковой процессор применяется программами при формировании различных аудио-эффектов. Принципиальная схема модуля, содержащего декодер и звуковой процессор, представлена на рис. 4.14.

Данные, считанные с компакт-диска, поступают на вход декодера IC305 (CXD1815), работающего совместно с процессором IC304 (SC430929PB). Эти две микросхемы преобразуют параллельный поток данных и корректируют возможные ошибки.

Для хранения данных декодер использует микросхему буферного ОЗУ IC303 емкостью 32 Кб с организацией 32Кх8.

К микросхеме звукового процессора CXD2925Q (IC308) подключено звуковое ОЗУ IC309 (М5М 44260CJ) объемом 512 Кб с организацией 256Кх16. В нем хранятся данные, необходимые при генерации звукового сопровождения. Подробно об этой области памяти рассказывалось в разделе, посвященном программной архитектуре звукового процессора приставки.

Возможности музыкального процессора позволяют использовать приставку SONY PLAYSTATION как бытовой проигрыватель музыкальных компакт-дисков. Для этого к выходу приставки рекомендуется подключить стационарный усилитель либо стереонаушники.

Цифровые аудиоданные последовательно передаются от звукового процессора на вход формирователя аудиосигнала IC402 (см. рис. 4.13). Эта микросхема представляет собой специализированный двухканальный 16-разрядный дельта-сигма ЦАП и работает с частотой дискретизации 44,1 кГц, что вполне достаточно для обеспечения качественного звучания.

Информация на ЦАП поступает по трем входам. На вход SDATA (вывод IC402/9) последовательно, бит за битом, приходят звуковые данные. Процесс передачи синхронизируется сигналом на входе BICK (вывод IC402/8). Уровень сигнала на входе LRCK (вывод IC402/10) определяет канал, для которого пересылаются данные (если на этом входе высокий уровень - передаются данные левого канала, если низкий - правого).

Работа формирователя аудиосигнала синхронизируется поступающим на вход MCLK (вывод IC402/6) тактовым сигналом частотой 16,9344 МГц.

Выходные сигналы левого и правого каналов звукового сопровождения снимаются с выходов микросхемы IC402 (выводы IС402/15,16) и поступают на выходной разъем CN502. Транзисторные ключи Q403 и Q404 используются для блокировки звука при нажатии кнопки RESET или при наличии сигнала высокого логического уровня на выводе IC308/37. 4.3.4. Модуль контроллера привода CD-ROM

На рис. 4.15 изображена принципиальная схема модуля контроллера CD-ROM и цепей его сопряжения с процессорной платой.

Три идентичных усилительных канала микросхемы IC702 (BA6392FP фирмы ROHM), специально предназначенной для проигрывателей CD и приводов CD-ROM, управляют сервоприводом объектива (L1, L2) и двигателем привода СГ (М2), а дифференциальный четвертый - двигателем вращения диска (Ml). Основные параметры BA6392FP таковы: напряжение питания 6-16 В, ток покоя 8-18 мА, мощность рассеивания 1,7 Вт, сопротивление нагрузок 8-20 Ом, выходное напряжение 1,3-5,2 В, коэффициент усиления канала вращения диска 8-13 дБ. В исходном состоянии, когда двигатели остановлены, напряжения на всех выходах BA6392FP одинаковы и близки к 3,5 В. В зависимости от разности напряжений на соответствующих выходах двигатели вращаются по часовой или против часовой стрелки.

Двигатель Ml контролируется комбинированным способом: грубо - изменением постоянной составляющей, точно - пачками разнополярных импульсов. Рабочее направление вращения диска - по часовой стрелке (при положительной разности напряжений на выводах 27 и 26 IC702). Открывание крышки привода CD-ROM вызывает экстренное торможение путем подачи на двигатель M1 напряжения обратной полярности.

Управление шаговым двигателем М2, перемещающим считывающую головку, только импульсное. Контакты выключателя S1 замыкаются, когда каретка СГ упирается в ограничитель. Система позиционирования считывающей головки получает сигнал, запрещающий дальнейшее передвижение СГ.

Коммутационные помехи подавляются фильтрами FB701 - FB704, а выбросы напряжения ограничиваются стабилитронами VD1 - VD4 с напряжением стабилизации 4,7 В.

Сервопривод объектива действует подобно динамической головке громкоговорителя, в которой звуковая катушка, находящаяся в поле постоянного магнита, движется под действием протекающего тока. Обмотки L1 и L2 сервопривода перемещают объектив во взаимно перпендикулярных плоскостях. Излучающий диод лазера А1 включен в коллекторную цепь транзистора Q701. Номинальная сила тока составляет 60-80 мА. Подстройка осуществляется резистором R1, входящим в цепь обратной связи САР-МЛ. Он расположен на гибком печатном ленточном кабеле, соединяющем СГ с вилкой CN702. При уменьшении сопротивления R1 сила тока и мощность излучения лазера увеличиваются. Сигналы, снимаемые с матрицы фототранзисторов А2, поступают на микросхему IC703 (A1791N) через разделительные конденсаторы СЗ — С6. Чувствительность устройства регулируется подстроечным резистором RV703. 4.3.5. Модуль адаптации

Назначение этого модуля — обеспечивать работу приставки с компакт-дисками как фирменного, так и нефирменного производства с маркировками «NTSC U/С» (США/Канада), «NTSC J» (Япония), «PAL» (Европа, Азия). Здесь применен 8-разрядный микроконтроллер Z86E0208PSC фирмы ZILOG с масочным ПЗУ объемом 512 байт (IC801), в которое при изготовлении заносится программа, представленная заказчиком. Тактовая частота 4,433 МГц равна частоте цветовой поднесущей в системе PAL и задается кварцевым резонатором Х801.

Принципиальная схема устройства показана на рис. 4.16.

В блоке использованы всего два выхода микроконтроллера. На первом из них (Q1) формируется синхропоследовательность для интерфейса CD-ROM, на втором (Q2) при включении питания генерируется импульс высокого логического уровня длительностью около 1 с.

Все элементы блока адаптации установлены на отдельной печатной плате, приклеенной к обратной стороне процессорной платы приставки и соединенной с ней проводами. В некоторых моделях PLAYSTATION вместо Z86E0208PSC применяется микроконтроллер 12С508/Р фирмы MICROCHIP TECHNOLOGY. |